**Universal Serial Bus Mass Storage Class**

# Control/Bulk/Interrupt (CBI) Transport

Revision 1.0 December 14, 1998

### **Technical Editors**

| Curtis E. Stevens | Phoenix Technologies Ltd. |

|-------------------|---------------------------|

| Mike Glass        | Microsoft Corporation     |

| Mark Williams     | Microsoft Corporation     |

| Jim Blackson      | Y-E Data, Inc.            |

### Contributors

| Pat LaVarreIomega CorporationDarrell RedfordIomega CorporationDuane KanzMicrosoft CorporationGlen SlickMicrosoft CorporationJordan BrownSun Microsystems, Inc.Paramita DasSun Microsystems, Inc.Mike ChenCMD TechnologyCalaimany BhoopathiShuttle TechnologyDave GilbertIn-System Design, Inc.David LukeIn-System Design, Inc.Eric LuttmanIn-System Design, Inc.Sadao YabukiTEAC System Create CorpMike NguyenTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationAlke PoulsenIomega CorporationAlker SenseHewlett-PackardAlker KeryPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-PackardTakashi MatsuiNanao | David G. Lawrence<br>Kenichi Hamada<br>Toyoko Shimizu<br>Ryota Okazaki<br>Shigeyoshi Hashi<br>Dominique L'Allement<br>Hiromichi Oribe<br>Yuji Oishi<br>Jon Eskdale<br>Tim Bradshaw | Global Technology Development<br>Y-E Data, Inc.<br>Y-E Data, Inc.<br>NEC Corporation<br>NEC Corporation<br>MGE<br>Hagiwara Sys-Com Co., Ltd.<br>Hagiwara Sys-Com Co., Ltd.<br>Iomega Corporation |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Darrell RedfordIomega CorporationDuane KanzMicrosoft CorporationGlen SlickMicrosoft CorporationJordan BrownSun Microsystems, Inc.Paramita DasSun Microsystems, Inc.Mike ChenCMD TechnologyCalaimany BhoopathiShuttle TechnologyDave GilbertIn-System Design, Inc.David LukeIn-System Design, Inc.Eric LuttmanIn-System Design, Inc.Sadao YabukiTEAC System Create CorpMike NguyenTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                            | Pat LaVarre                                                                                                                                                                        |                                                                                                                                                                                                  |

| Glen SlickMicrosoft CorporationJordan BrownSun Microsystems, Inc.Paramita DasSun Microsystems, Inc.Mike ChenCMD TechnologyCalaimany BhoopathiShuttle TechnologyDave GilbertIn-System Design, Inc.David LukeIn-System Design, Inc.Eric LuttmanIn-System Design, Inc.Sadao YabukiTEAC System Create CorpMike NguyenTEAC America, Inc.Tsuyoshi OsawaTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                 | Darrell Redford                                                                                                                                                                    |                                                                                                                                                                                                  |

| Jordan BrownSun Microsystems, Inc.Paramita DasSun Microsystems, Inc.Mike ChenCMD TechnologyCalaimany BhoopathiShuttle TechnologyDave GilbertIn-System Design, Inc.David LukeIn-System Design, Inc.Eric LuttmanIn-System Design, Inc.Sadao YabukiTEAC System Create CorpMike NguyenTEAC America, Inc.Tsuyoshi OsawaTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                | Duane Kanz                                                                                                                                                                         | • •                                                                                                                                                                                              |

| Paramita DasSun Microsystems, Inc.Mike ChenCMD TechnologyCalaimany BhoopathiShuttle TechnologyDave GilbertIn-System Design, Inc.David LukeIn-System Design, Inc.Eric LuttmanIn-System Design, Inc.Sadao YabukiTEAC System Create CorpMike NguyenTEAC America, Inc.Tsuyoshi OsawaTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                | Glen Slick                                                                                                                                                                         | Microsoft Corporation                                                                                                                                                                            |

| Mike ChenCMD TechnologyCalaimany BhoopathiShuttle TechnologyDave GilbertIn-System Design, Inc.David LukeIn-System Design, Inc.Eric LuttmanIn-System Design, Inc.Sadao YabukiTEAC System Create CorpMike NguyenTEAC America, Inc.Tsuyoshi OsawaTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                    | Jordan Brown                                                                                                                                                                       | Sun Microsystems, Inc.                                                                                                                                                                           |

| Calaimany BhoopathiShuttle TechnologyDave GilbertIn-System Design, Inc.David LukeIn-System Design, Inc.Eric LuttmanIn-System Design, Inc.Sadao YabukiTEAC System Create CorpMike NguyenTEAC America, Inc.Tsuyoshi OsawaTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                           | Paramita Das                                                                                                                                                                       | Sun Microsystems, Inc.                                                                                                                                                                           |

| Dave GilbertIn-System Design, Inc.David LukeIn-System Design, Inc.Eric LuttmanIn-System Design, Inc.Sadao YabukiTEAC System Create CorpMike NguyenTEAC America, Inc.Tsuyoshi OsawaTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationDavid JolleyIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                           | Mike Chen                                                                                                                                                                          | CMD Technology                                                                                                                                                                                   |

| David LukeIn-System Design, Inc.Eric LuttmanIn-System Design, Inc.Sadao YabukiTEAC System Create CorpMike NguyenTEAC America, Inc.Tsuyoshi OsawaTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                             | Calaimany Bhoopathi                                                                                                                                                                | Shuttle Technology                                                                                                                                                                               |

| Eric LuttmanIn-System Design, Inc.Sadao YabukiTEAC System Create CorpMike NguyenTEAC America, Inc.Tsuyoshi OsawaTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                | Dave Gilbert                                                                                                                                                                       | In-System Design, Inc.                                                                                                                                                                           |

| Sadao YabukiTEAC System Create CorpMike NguyenTEAC America, Inc.Tsuyoshi OsawaTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                               | David Luke                                                                                                                                                                         | In-System Design, Inc.                                                                                                                                                                           |

| Mike NguyenTEAC America, Inc.Tsuyoshi OsawaTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                  | Eric Luttman                                                                                                                                                                       | In-System Design, Inc.                                                                                                                                                                           |

| Tsuyoshi OsawaTEAC CorporationSteven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                               | Sadao Yabuki                                                                                                                                                                       |                                                                                                                                                                                                  |

| Steven SmitheTEK LabsMike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Mike Nguyen                                                                                                                                                                        | TEAC America, Inc.                                                                                                                                                                               |

| Mike LeiboweTEK LabsYoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationDavid JolleyIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Tsuyoshi Osawa                                                                                                                                                                     | TEAC Corporation                                                                                                                                                                                 |

| Yoshitaka OtaKonicaAlbert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationDavid JolleyIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Steven Smith                                                                                                                                                                       | eTEK Labs                                                                                                                                                                                        |

| Albert SaraieSicore SystemsTrenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationDavid JolleyIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Mike Leibow                                                                                                                                                                        | eTEK Labs                                                                                                                                                                                        |

| Trenton HenryStandard Microsystems CorporationBill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationDavid JolleyIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Yoshitaka Ota                                                                                                                                                                      | Konica                                                                                                                                                                                           |

| Bill StanleyAdaptecShing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationDavid JolleyIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Albert Saraie                                                                                                                                                                      | Sicore Systems                                                                                                                                                                                   |

| Shing F. LinAdaptecAlex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationDavid JolleyIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Trenton Henry                                                                                                                                                                      | Standard Microsystems Corporation                                                                                                                                                                |

| Alex AfsharMatsushita SemiconductorJames QuigleyIomega CorporationMike PoulsenIomega CorporationDavid JolleyIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bill Stanley                                                                                                                                                                       | Adaptec                                                                                                                                                                                          |

| James QuigleyIomega CorporationMike PoulsenIomega CorporationDavid JolleyIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Shing F. Lin                                                                                                                                                                       | Adaptec                                                                                                                                                                                          |

| Mike PoulsenIomega CorporationDavid JolleyIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Alex Afshar                                                                                                                                                                        | Matsushita Semiconductor                                                                                                                                                                         |

| David JolleyIomega CorporationAl RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | James Quigley                                                                                                                                                                      | Iomega Corporation                                                                                                                                                                               |

| Al RickeyPhoenix Technologies Ltd.Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Mike Poulsen                                                                                                                                                                       | Iomega Corporation                                                                                                                                                                               |

| Mark McCoyAnchor Chips Inc.Steve BaylessHewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | David Jolley                                                                                                                                                                       | Iomega Corporation                                                                                                                                                                               |

| Steve Bayless Hewlett-Packard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Al Rickey                                                                                                                                                                          | Phoenix Technologies Ltd.                                                                                                                                                                        |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Mark McCoy                                                                                                                                                                         | Anchor Chips Inc.                                                                                                                                                                                |

| Takashi Matsui Nanao                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Steve Bayless                                                                                                                                                                      | Hewlett-Packard                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Takashi Matsui                                                                                                                                                                     | Nanao                                                                                                                                                                                            |

#### USB Mass Storage Class CBI Transport Specification Copyright © 1998, USB Implementers Forum. All rights reserved.

#### INTELLECTUAL PROPERTY DISCLAIMER

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE.

A LICENSE IS HEREBY GRANTED TO REPRODUCE AND DISTRIBUTE THIS SPECIFICATION FOR INTERNAL USE ONLY. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY OTHER INTELLECTUAL PROPERTY RIGHTS IS GRANTED OR INTENDED HEREBY.

AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF PROPRIETARY RIGHTS, RELATING TO IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. AUTHORS OF THIS SPECIFICATION ALSO DO NOT WARRANT OR REPRESENT THAT SUCH IMPLEMENTATION(S) WILL NOT INFRINGE SUCH RIGHTS.

Please send comments via electronic mail to techsup@usb.org

## **Table of Contents**

| 1. |    | Intr | oduc | ction                                           | 6  |

|----|----|------|------|-------------------------------------------------|----|

|    | 1. | 1    | Sco  | pe                                              | 6  |

|    | 1. | 2    | Targ | get Audience                                    | 7  |

|    | 1. | 3    | Purp | Dose                                            | 7  |

|    | 1. | 4    | Terr | ns and Abbreviations                            | 7  |

|    |    | 1.4. | 1    | Terms from the USB Specification                | 7  |

|    |    | 1.4. | 2    | Terms Adapted from the SPC-2 Specification      | 8  |

|    |    | 1.4. | 3    | Terms Specific to this Specification            | 8  |

|    |    | 1.4. | 4    | Key Cross References to USB Core Specifications | 9  |

|    | 1. | 5    | Bus  | Trace Notation Conventions                      | 0  |

| 2. |    | Fun  | ctio | nal Characteristics1                            | 1  |

|    | 2. | 1    | Port | Reset Protocol1                                 | 1  |

|    | 2. | 2    | Con  | nmand Block Reset Protocol1                     | 11 |

|    | 2. | 3    | Non  | -Data Command Protocol 1                        | 12 |

|    |    | 2.3. | 1    | Command Transport for Non-Data Commands 1       | 12 |

|    |    | 2.3. | 2    | Status Transport for Non-Data Commands 1        | 3  |

|    | 2. | 4    | Data | a In Command Protocol                           | 15 |

|    |    | 2.4. | 1    | Command Transport for Data In Commands          | 15 |

|    |    | 2.4. | 2    | Data In Transport 1                             | 15 |

|    |    | 2.4. | 3    | Status Transport for Data In Commands 1         | 6  |

|    | 2. | 5    | Data | a Out Command Protocol 1                        | 17 |

|    |    | 2.5. | 1    | Command Transport for Data Out Commands         | 17 |

|    |    | 2.5. | 2    | Data Out Transport1                             | 17 |

|    |    | 2.5. | 3    | Status Transport for Data Out Commands 1        | 17 |

|    | 2. | 6    | Unic | directional Data Transport Requirement          | 17 |

| 3. |    | Sta  | ndar | d Descriptors 1                                 | 8  |

|    | 3. | 1    | Dev  | ice Descriptor 1                                | 8  |

|    | 3. | 2    | Con  | figuration Descriptor1                          | 9  |

|    | 3. | 3    | Inte | rface Descriptors                               | 20 |

|    | 3. | 4    | End  | point Descriptors2                              | 21 |

|    |    | 3.4. | 1    | Bulk In Endpoint                                | 21 |

|    |    | 3.4. | 2    | Bulk Out Endpoint                               | 22 |

|    |    | 3.4. | 3    | Interrupt Endpoint                              | 22 |

| 4. |    | Rec  | lues | ts                                              | 25 |

|    | 4. | 1    | Clas | ss-Specific Requests                            | 25 |

## List of Tables

| Figure 1 - Sample Descriptor Organization                               | 6  |

|-------------------------------------------------------------------------|----|

| Table 2.1 – Example of an ADSC Class-Specific Request                   | 13 |

| Table 2.2 – Example of Command Block Status Transport by Interrupt Pipe | 14 |

| Table 3.1 - Device Descriptor                                           | 18 |

| Table 3.2 - Configuration Descriptor                                    | 19 |

| Table 3.3 - Data Interface Descriptor                                   | 20 |

| Table 3.4 - Bulk In Endpoint Descriptor                                 | 21 |

| Table 3.5 - Bulk Out Endpoint Descriptor                                | 22 |

| Table 3.6 - Interrupt Endpoint Descriptor                               | 22 |

| Table 3.7 – Interrupt Data Block                                        | 23 |

| Table 3.8 – Interrupt Data Block for bInterfaceSubClass = 04h           | 24 |

| Table 4.1 - Accept Device-Specific Command                              | 25 |

| Table 4.2 - ADSC bmRequestType                                          | 25 |

### 1. Introduction

The Universal Serial Bus (USB) is a communications architecture that gives a PC the ability to interconnect a variety of devices via a simple four-wire cable. The USB is actually a two-wire serial communication link that runs at 12 megabits (Mbs) per second. USB protocols can configure devices at startup or when they are plugged in at run time.

How devices on the USB bus behave is the subject of this and other USB Device Class Specifications.

Devices in a given class can be broken into subclasses. These divisions allow software to search the bus and select all of the devices that it can control. Each device can have one or more configurations that define how the device functions. A device that can function in several different ways will have a configuration for each function. A *configuration* is a collection of interfaces. An *interface* specifies which hardware in the device will interact with the USB. Each of these pieces of hardware is called an *endpoint*. Therefore, an interface is a collection of endpoints (for each *alternate setting* of the interface). The USB Device Class Definitions define the default configurations, interfaces, alternate settings, and endpoints that a device in a given class or subclass should provide.

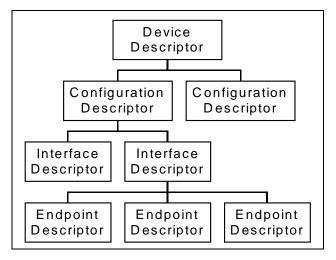

A *descriptor* describes general information about a device, configuration, interface, or endpoint. Figure 1 shows the hierarchical organization of USB descriptors.

Figure 1 - Sample Descriptor Organization

#### 1.1 Scope

• A familiarity with the USB 1.0 and 1.1 specifications is assumed.

This specification addresses the **Control/Bulk/Interrupt** (**CBI**) **architecture**, in which the Control, Bulk In/Out and Interrupt endpoints are used for communication between the host and device. That is, the Control endpoint is used to transport command blocks to the device via a class-specific request, as well as to transport standard USB requests. The Bulk In and Bulk Out endpoints are used to transport data between the host and the device. The Interrupt endpoint is used to signal command completion.

This specification assumes the host complies with the USB v1.0 and v1.1 specifications. Nothing in this specification, in its original intent, contradicts the USB v1.0 and v1.1 specifications.

### **1.2 Target Audience**

The CBI and Bulk-Only specifications are each intended to be stand-alone documents for the USB Mass Storage sub-class, enabling development of a USB Mass Storage compliant device. A device manufacturer *may* choose to implement both CBI and Bulk-Only, but shall follow each specification as applicable.

The Bootability specification is considered an enhancement to either the CBI or Bulk-Only specifications. Devices *may* be CBI only, Bulk-Only, and not be Bootable. However, to be bootable, the device must comply with the Bootability specification, as well as the CBI specification or the Bulk-Only specification or both.

#### 1.3 Purpose

The purpose of this document is to provide some common descriptions of the USB configuration, interface, and endpoint descriptors, as well as a communications protocol, for operating system, BIOS, and peripheral designers implementing support for CBI mass storage devices. Subclasses are defined that associate device types with industry standard command block definitions. This specification shows how command blocks are delivered to a device and what the device response will be. This provides a framework for designing the peripherals of a given type or subclass.

#### 1.4 Terms and Abbreviations

This section defines important terms used in other sections of this specification. Some of the term definitions are copied from other specifications, such as the *Universal Serial Bus Specification* or the SCSI *Primary Commands* – 2 (SPC-2) specifications.

#### 1.4.1 Terms from the USB Specification

The following term definitions are copied from the *Universal Serial Bus Specification*, 1.0 revision, for the convenience of the reader.

| ACK                    | Handshake packet indicating a positive acknowledgment.                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Class Specific Request | All USB devices respond to requests from the host on the device's default pipe. These transfers are made using control transfers. A request is contained in the data portion of a SETUP packet. The <i>Universal Serial Bus Specification</i> defines a set of standard requests for all USB devices. When a class of devices is defined, requests specific to that class of devices, which extend the standard requests, can be defined. |

| Control Transfer       | One of four Universal Serial Bus transfer types. Control transfers<br>support configuration/command/status type communications between<br>client and function.                                                                                                                                                                                                                                                                            |

| Endpoint Address       | The combination of a Device Address and an Endpoint Number on a USB device.                                                                                                                                                                                                                                                                                                                                                               |

| Endpoint Number        | A unique pipe endpoint on a USB device.                                                                                                                                                                                                                                                                                                                                                                                                   |

| NAK                    | Handshake packet indicating a negative acknowledgment.                                                                                                                                                                                                                                                                                                                                                                                    |

| Stage                  | One part of the sequence composing a control transfer; i.e., the setup stage, the data stage, and the status stage.                                                                                                                                                                                                                                                                                                                       |

| 1.4.2 Terms Adapted from the     | SPC-2 Specification                                                                                                                                                                                                                                                                     |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ASC                              | An acronym for Additional Sense Code. A device uses ASCs to provide additional detail describing the Sense Key.                                                                                                                                                                         |  |

| ASCQ                             | An acronym for Additional Sense Code Qualifier. A device uses ASCQs to provide further detail describing the ASC.                                                                                                                                                                       |  |

| Command Block                    | Also called Command Descriptor Block. A structure defined by the command set used to communicate commands from the host to the device. The command block is carried by an ADSC over the USB during Command Block Transport.                                                             |  |

| Immediate Command Block          | A Command Block which has an immediate bit set, typically starting a long-running operation at the device. The device returns preliminary status information to the host via Status Transport as soon as the command block has been validated.                                          |  |

| Sense Data                       | Data describing an error or exceptional device condition that a device delivers to the host.                                                                                                                                                                                            |  |

| SK                               | An acronym for Sense Key. A device reports generic categories of error<br>and exception conditions in the Sense Key. The host can use the Sense<br>Key information to select high-level error recovery procedures.                                                                      |  |

| Unit Attention Condition         | A state that a device maintains while it has asynchronous status<br>information to report to the host. This is not the same as a Persistent<br>Command Block failure.                                                                                                                   |  |

| Unrecoverable Error              | A condition in which the device cannot complete the command such as<br>no media, device failure, etc. This is one reason but not the only reason<br>for Command Block failure.                                                                                                          |  |

| 1.4.3 Terms Specific to this Spe | cification                                                                                                                                                                                                                                                                              |  |

| ADSC                             | Acronym for the Accept Device Specific Command class-specific request. The ADSC is the USB wrapper that surrounds a Command Block when transported across the USB.                                                                                                                      |  |

| Clear stall                      | Use of the USB standard Clear Feature request with the standard ENDPOINT_HALT feature selector. In other words, a Clear Feature (ENDPOINT_HALT) request issued by the host.                                                                                                             |  |

| Command                          | Not a useful term in this specification. Use the more specific terms<br>Command Block or USB request.                                                                                                                                                                                   |  |

| Command Block Failure            | The condition where a Command Block has completed with a<br>Command Block Status of Failed. This is not the same as Command<br>Transport failure. A stall in Command Block Transport is one way for<br>the device to signal Command Block Failure to the host, but not the<br>only way. |  |

| Command Block Status             | Either In-progress, Passed, or Failed                                                                                                                                                                                                                                                   |  |

| Command Block Transport | In general, Command Block Transport is the way the host sends a Command Block to the device.                                                    |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Final Status            | Whether a long running operation begun by an Immediate Command<br>Block is In-progress, or has Passed, or has Failed                            |

| May                     | A keyword that indicates an option.                                                                                                             |

| Ор                      | Operation code. A two-digit hexadecimal value defined by the command set indicating the command encoded in a Command Block.                     |

| Phase Error             | The result of the device and the host disagreeing on expected data transfer size and/or direction.                                              |

| Preliminary Status      | Not the final status, but rather merely the Command Block Status of an Immediate Command Block                                                  |

| Shall                   | A keyword that indicates a requirement.                                                                                                         |

| Should                  | A keyword that indicates flexibility of choice with a strongly preferred<br>alternative; equivalent to the phrase "it is strongly recommended". |

| Status Transport        | In general, Status Transport is the way a device sends status to the host.                                                                      |

#### 1.4.4 Key Cross References to USB Core Specifications

This section provides cross-references to key sections of the *USB Specification*, v1.1. The referenced sections of the USB Specification describe rules and concepts that are useful in understanding this specification.

| Disallow STALL of Setup Stage of Control Transfer | See sections 5.5.5 and 8.5.2 of the USB Specification, v1.1 |

|---------------------------------------------------|-------------------------------------------------------------|

| Port Reset                                        | See section 10.2.8.1 of the USB Specification, v1.1.        |

#### **1.5 Bus Trace Notation Conventions**

This section outlines the conventions used for gathering bus traces from devices designed using the Control-Bulk-Interrupt USB Mass Storage specification as shown in chapter 2.

Basic conventions used:

- The letter lowercase letter "x" prefixes hexadecimal numbers.

- The ":" (colon) and " " (blank) are interchangeable. Colons associate together, visually in a trace, the bytes of a multi-byte field.

- EOP is implied, though not shown, by the trailing ")" parenthesis in the form "DATA(x XX XX ...)"

- "DATA()" is an empty packet (i.e. just EOP from the host Out or from the device In, no other data).

- USB PIDs shown include SOF ACK NAK STALL SETUP OUT IN DATA0 DATA1.

- The bits of a PID can appear in time order of the bus, or reversed.

- ADDR(x7F) is just an example of a device address. x00 to x7F may be valid the host chooses this value during enumeration.

- ENDP(x1) is just an example of a bulk IN endpoint number. ENDP(x2) is just an example of a bulk OUT endpoint number. ENDP(x3) is just an example of an interrupt endpoint number. x1 to x1F may be valid the device reports this value during enumeration. Because the endpoint number and the direction together form a distinct endpoint address, the endpoint number may be the same for bulk IN and bulk OUT, or for interrupt IN and bulk OUT. ENDP(x0) is the required default control endpoint number.

- The choice of DATA0 and DATA1 are examples. Bulk and interrupt traffic in particular often begin with one or the other. The *USB Specification* gives rules for when the host changes its choice of this "data toggle" and how the device responds to the two different choices at different times.

- NAK in examples shows the possibility of the NAK, without requiring that NAK.

- Repeat of NAK is not shown.

- SOF in examples shows the possibility of the SOF, without requiring that SOF.

- IDLE is not shown.

- Bit-stuffing, CRCs, and idle times are not shown.

- No babble shown, no violation of *MaxPacketSize* of endpoint shown.

### **2. Functional Characteristics**

The host and mass storage devices communicate over the USB using the protocols described by this specification. These protocols are based on the command/data/status style of communication. That is, the protocols transport command blocks from the host to the device; transport data between the host and device; transport "status" of the command block from the device to the host; and allow the host to reset the device.

Mass storage devices shall accept two types of resets and three types of command blocks.

The two types of resets are:

- Port Reset

- Command Block Reset

The three types of command blocks are:

- Non-Data

- Data-In

- Data-Out

The three types of command blocks, with their respective protocols, including status and error reporting, are covered below. The host decides which protocol to try. The device then decides whether to cooperate. The "Status" of a command block is given by the device and is one of In-Progress, Passed, or Failed.

This specification does not define how the device responds if the host fails to comply with the requirements of this specification (often expressed using the phrase "the host shall ..."). A host that discovers it has violated protocol inadvertently should reset the device.

#### 2.1 Port Reset Protocol

See the USB Specification.

If a mass storage device does not respond as outlined in this specification, the host may resort to a port reset of the offending device.

WARNING: Using Port Reset to abort an In-Progress command may result in the loss of data.

#### 2.2 Command Block Reset Protocol

Before taking the drastic action of a Port Reset, the host may first try a Command Block Reset.

To issue a Command Block Reset, the host shall use the Non-Data Command Protocol to transport the command block:

1Dh 04h FFh FFh FFh FFh ...

The device may use the trailing FFh bytes to distinguish the Command Block Reset from the legacy op 1Dh SEND DIAGNOSTIC command block.

Upon receipt of a Command Block Reset, the device shall

- 1. Attempt to abort any currently executing command or data transfer;

- 2. Drop any command blocks that may be queued for execution;

- 3. Discard any data buffered at the device;

- 4. Reset the mass storage portion of the device, as described in the corresponding industry standard documents indicated by the *bInterfaceSubClass* field (i.e. perform a self-test, initialize the device's operating modes to there default conditions);

- 5. Clear any persistent command block failure condition.

After a Command Block Reset completes, the Stall condition and data toggle of the device's endpoints are undefined. The host shall send a Clear Feature (ENDPOINT\_HALT) USB standard request to both the Bulk In and Bulk Out pipes to clear any Stall conditions and reset the data toggles.

WARNING: Using Command Block Reset to abort an In-Progress command may result in the loss of data.

#### 2.3 Non-Data Command Protocol

The host shall use the Non-Data Command Protocol to transport a command block and its status with no accompanying data.

#### 2.3.1 Command Transport for Non-Data Commands

The host shall send each command block to the device via a Control Transfer to the default control pipe (endpoint number zero). The host shall begin the Command Transport with a class-specific request (the ADSC). The host shall send the Command Transport Data in the Data Stage of the Control Transfer. The Command Transport is completed with the completion of the Status Stage of the Control Transfer.

The format, length, and padding of the command block is defined by the command set of the device, as indicated by the Subclass code (see the USB Mass Storage Class Specification Overview.).

According to the USB Specification, the host shall fragment the command block and toggle between DATA0 and DATA1 as needed to respect the MaxPacketSize reported in the Device descriptor.

The device may delay Command Transport indefinitely by NAK in the Data Stage and/or Status Stage of the Control Transfer, subject to the limitations expressed in the rest of this specification.

Note: The previous paragraph states a class-specific exemption to the USB Specification.

The device may fail the Command Transport by STALL in the Data Stage or Status Stage of the Control Transfer. Else the device shall accept the Command Transport Data by ACK in the Data Stage and Status Stage of the Control Transfer.

Successful transport of Command Transport Data does not necessarily imply the status of the command block contained therein is Passed. See the discussion of Status Transport.

Table 2.1 shows an example of the ADSC class-specific request.

```

1

SOF(xA5)

2

SETUP(xB4) ADDR(x7F) ENDP(x0)

3

DATA0(xC3) DATA(x 21 00 00:00 00:00 0C:00)

4

ACK(x4B)

5

SOF(xA5)

6

OUT(x87) ADDR(x7F) ENDP(x0)

7

DATA1(xD2) DATA(x 2A 00 00:01:23:45 00 00:)

8

NAK(x5A)

9

SOF(xA5)

10

OUT(x87) ADDR(x7F) ENDP(x0)

11

DATA1(xD2) DATA(x 2A 00 00:01:23:45 00 00:)

12

ACK(x4B)

13

SOF(xA5)

14

DATA0(xC3) DATA(x 00 00 00:00)

15

NAK(x5A)

16

SOF(xA5)

OUT(x87) ADDR(x7F) ENDP(x0)

17

DATA0(xC3) DATA(x 00 00 00:00)

18

19

ACK(x4B)

20

SOF(xA5)

IN(x96) ADDR(x7F) ENDP(x0)

21

22

NAK(x5A)

23

SOF(xA5)

24

IN(x96) ADDR(x7F) ENDP(x0)

25

DATA1(xD2) DATA(

)

26

ACK(x4B)

```

Table 2.1 – Example of an ADSC Class-Specific Request

USB requires the device to ACK the Setup Stage. The device may STALL in place of the ACKs of the Data Stage or Status Stage to indicate command block failure.

#### 2.3.2 Status Transport for Non-Data Commands

To indicate a command block is In-progress, the device shall NAK the appropriate endpoint, as described below. To indicate a command block has passed, the device shall ACK the appropriate endpoint and may supply status bytes by interrupt pipe, as specified in section 2.3.2.2. To indicate a command block has failed, the device shall STALL a pipe or supply status bytes by interrupt pipe, or both. Details follow.

#### 2.3.2.1 Status Transport by Control Pipe

The device may choose to transport command block status by control pipe.

The device may NAK the Data Stage and/or the Status Stage of the ADSC class-specific request to indicate a command block is In-Progress. But an ACK of the Status Stage does not mean command block complete; that ACK only means the command block transport has completed.

The device may STALL the Data Stage and/or the Status Stage of the ADSC class-specific request to indicate a command block has Failed. If the device does STALL an ADSC, then the device shall not transport the status for the command block transported by the stalled ADSC by interrupt pipe – thus the host shall not wait for command block status to appear there.

Table 2.1 of Command Transport shows an example of the transport of In-Progress command block status by control pipe. The device may STALL in place of any of the NAKs of that example to transport Failed command block status.

#### 2.3.2.2 Status Transport by Interrupt Pipe

This section applies to devices that implement command completion interrupts.

After successful completion of Command Transport, the device may NAK the interrupt pipe (in response to IN PID) to indicate a command block is In-Progress.

If and when the command block status changes from In-progress to Passed or Failed, the device shall then return status bytes on the Interrupt endpoint. The status bytes returned depend on the command set, as described in Chapter 3.

The command set defines whether or not any bulk data transported for a command block is valid if the command block fails. When a command block fails, the bulk data transported prior to the failure may or may not be valid, as defined in the command set.

Table 2.2 shows an example of the transport of command block status by interrupt pipe.

#### Table 2.2 – Example of Command Block Status Transport by Interrupt Pipe

```

1 SOF(xA5)

2 IN(x96) ADDR(x7F) ENDP(x3)

3 NAK(x5A)

4 SOF(xA5)

5 IN(x96) ADDR(x7F) ENDP(x3)

6 DATA1(xD2) DATA(xFF:FF)

7 ACK(x4B)

```

#### 2.3.2.3 Host Violation of Status Transport Protocol

If the host does not poll the Interrupt endpoint and proceeds to send another ADSC, the device shall clear the still pending interrupt when the device accepts the ADSC.

#### 2.3.2.4 Indefinite Delay

The device may NAK indefinitely, for example, when the device interprets a command block as a request to move data, but the host does not move data. In this case, the host shall time out the offending request and reset the device as described by this specification. How long the host waits before timing out is command set dependent.

Table 2.1 of Command Transport and Table 2.2 of Status Transport by Interrupt Pipe show where NAK may appear, thus where indefinite NAK may appear.

#### 2.3.2.5 Status Transport for Immediate Command Blocks

Some command sets define both non-immediate and immediate command blocks. Immediate command blocks transport "preliminary status" as soon as the device is ready to interpret another command block. The Immediate command block may begin a long-running operation in the device. The device shall transport the preliminary status using the Status Transport defined herein. The command set defines how the final status of the Immediate command is transported.

#### 2.3.2.6 Persistent Command Block Failure

After the device fails a command block, the device may continue to fail every command block received until the host either supplies a command block that clears this Persistent Command Block Failure, performs a Command Block Reset, performs a USB Suspend, or performs a Port Reset.

The command set defines

- Which errors persist and which do not;

- Which command blocks, if any, clear a Persistent Command Block Failure;

- Whether such a command block proceeds to execute as normal;

- Which command blocks may complete successfully without disturbing an otherwise Persistent Command Block Failure.

While making a command block failure persist, the device may transport the failed status using any of the normal mechanisms. That is, the device may ACK the transport of a command block and then fail the command block later.

While making a command block failure persist, the device may change the ASC/ASCQ values transported by interrupt pipe.

Because a USB Suspend may deny power to a bus-powered device, the device may forget a Persistent Command Block Failure in response to a USB Suspend.

#### 2.4 Data In Command Protocol

The host shall use the Data-In Command Protocol to transport a command block, read data in from a device, and transport the command block status.

#### 2.4.1 Command Transport for Data In Commands

See section 2.3.1 Command Transport for Non-Data Commands.

#### 2.4.2 Data In Transport

#### 2.4.2.1 Data In: Normal Operation

The host shall send the IN PID to the Bulk In endpoint to request transport of data in from the device. The host shall continue to send IN PID until it receives the amount of data expected.

The device shall NAK until it has data available. When data becomes available, the device shall supply data in *MaxPacketSize* packets, as described in the USB specification. If the supply of data is temporarily exhausted, the device shall again NAK until data becomes available.

If the device supplies a zero-length or short packet, the host should consider the transport of data for the current command block to have ended, and send no more IN PID.

The device shall send a zero-length or short packet as the last packet only if the total amount of data supplied is less than that expected by the host. The device shall send a short, but not a zero-length, last packet if the amount of data remaining does not completely fill a Bulk In packet. The device shall not send a zero-length packet if the total amount of data supplied exactly matches that expected by the host and is a multiple of *MaxPacketSize*.

#### 2.4.2.2 Data In: Short Transfer, Normal Operation

The command set may define legitimate cases where the device supplies less data than requested by the host, for example, op 5Ah MODE SENSE command. In this condition, the device shall send a zero-length or short packet to identify the end of the data.

If the device supplies a zero-length or short packet, the host should consider the transport of data for the current command block to have ended, and send no more IN PID.

#### 2.4.2.3 Data In: Host Requests Too Few Bytes

If the host sends less IN PID than the device expects, the device cannot know if the host has stopped transporting data or if the host is just remarkably slow. Therefore, in this case, the device may NAK the transport of status indefinitely.

#### 2.4.2.4 Data In: Data Overrun within Packet

If the device sends more data in one packet than the host expects, the host may reset the device as described by this specification.

#### 2.4.2.5 Data In: Host Requests Too Many Bytes

If the host sends more IN PID than the device can satisfy, then the device may NAK indefinitely (for more information, see section 2.3.2.4). The device should STALL (see section 2.4.3).

#### 2.4.2.6 Data In: Perhaps the Wrong Bytes

The device may detect an error after all data has been successfully transported, in which case the device shall indicate the error in the Status Transport. The host shall read the Status Transport to determine the validity of the data.

#### 2.4.3 Status Transport for Data In Commands

See section 2.3.2 Status Transport for Non-Data Commands.

#### 2.4.3.1 Status Transport by Bulk Pipe

#### 2.4.3.1.1 Do Not Report Stalled ADSC

If the device reports the command block status by STALL of the ADSC class-specific request, the device shall not report that status again by interrupt pipe nor by bulk pipe. That is, the device shall not make command completion status available by interrupt and the device shall not stall either bulk endpoint.

#### 2.4.3.1.2 Status by Bulk In Pipe

The device may choose to report status by Bulk In pipe in addition to reporting status by Status Transport as described by this specification (see section 2.3.2).

The device may NAK the Bulk In endpoint (in response to an IN PID respectively) to indicate a command block is In-Progress.

The device may STALL the Bulk In pipe to indicate a command block has failed.

#### 2.4.3.1.3 Clearing a Bulk In Pipe Stall

According to the *USB Specification*, the host shall respond to a STALL of the Bulk In pipe by the device with a Clear Feature of Endpoint Halt to clear the Stall and reset the data toggle to DATA0.

A device may STALL the Bulk In pipe AFTER the last data has transferred. For this reason the host shall also issue Clear Feature for Endpoint Halt to the Bulk In pipe if the device reports that the Data In command block has Failed.

#### 2.5 Data Out Command Protocol

The host shall use the Data-Out Command Protocol to transport a command block, write data out to the device, and transport the command block status.

#### 2.5.1 Command Transport for Data Out Commands

See section 2.3.1 Command Transport for Non-Data Commands.

#### 2.5.2 Data Out Transport

#### 2.5.2.1 Data Out: Normal Operation

The host shall send the OUT PID to the Bulk Out endpoint to request to transport data out to the device.

The device may ACK to accept data. If the host supplies a short packet, the device should consider the transport of data for the current command block to have ended.

The device shall NAK until it has buffer available to accept data.

#### 2.5.2.2 Data Out: Host Sends Too Few Bytes

If the host sends less OUT PID than the device expects, the device cannot know if the host has stopped transporting data or if the host is just slow. Therefore, in this case, the device may NAK the transport of status indefinitely.

#### 2.5.2.3 Data Out: Host Sends Too Many Bytes

If the host sends more OUT PID than the device can accept, then the device may NAK indefinitely, STALL the Bulk Out pipe, or ACK the data in an implementation-specific manner.

#### 2.5.3 Status Transport for Data Out Commands

See section 2.4.3, except Bulk In reads as Bulk Out.

#### 2.6 Unidirectional Data Transport Requirement

The command sets applied to this specification shall not define a command block that requires data to be transferred on both the Bulk In and Bulk Out pipes.

### **3. Standard Descriptors**

CBI mass storage devices shall support the following standard USB descriptors:

- **Device**. Each device has one device descriptor.

- **Configuration**. Each device has one default configuration descriptor, which supports at least one interface.

- **Interface**. CBI mass storage devices shall support at least a Data interface. Some devices may support additional interfaces based on their control and isochronous capabilities.

- **Endpoint**. CBI mass storage devices shall support the following endpoints, in addition to the Endpoint 0 for control transfers that is required of all USB devices:

- Bulk In endpoint. CPU data transfers.

- Bulk Out endpoint. CPU data transfers.

- Interrupt endpoint. Command completion interrupt, required if *bInterfaceProtocol* is 00h.

CBI mass storage devices have no class-specific descriptors.

The rest of this section describes the standard USB device, configuration, interface, and endpoint descriptors for CBI mass storage devices. For information about other standard descriptors, see Chapter 9, "USB Device Framework," of the *USB Specification*.

#### **3.1 Device Descriptor**

There is only one Device Descriptor for each USB device. Note that for a Mass Storage class device, the device class and subclass codes are not specified in the Device descriptor, but in the Interface descriptor (for more information, see section 3.3).

| Offset | Field           | Size | Value | Description                                                |

|--------|-----------------|------|-------|------------------------------------------------------------|

| 0      | bLength         | Byte | 12h   | Size of this descriptor in bytes.                          |

| 1      | bDescriptorType | Byte | 01h   | DEVICE descriptor type.                                    |